- CCC cu valoare de 560 pF (pag.1 - Arbitrul de memorie şi logica de comandă),

- C49 cu valoare de 330 pF (pag.3 - Circuitul de configurare şi selecţie, la modificarea de 80K)

Absenţa acestui condensator provoca manifestări în Basic şi Devil de genul celor surprinse în screenshot-urile de mai jos:

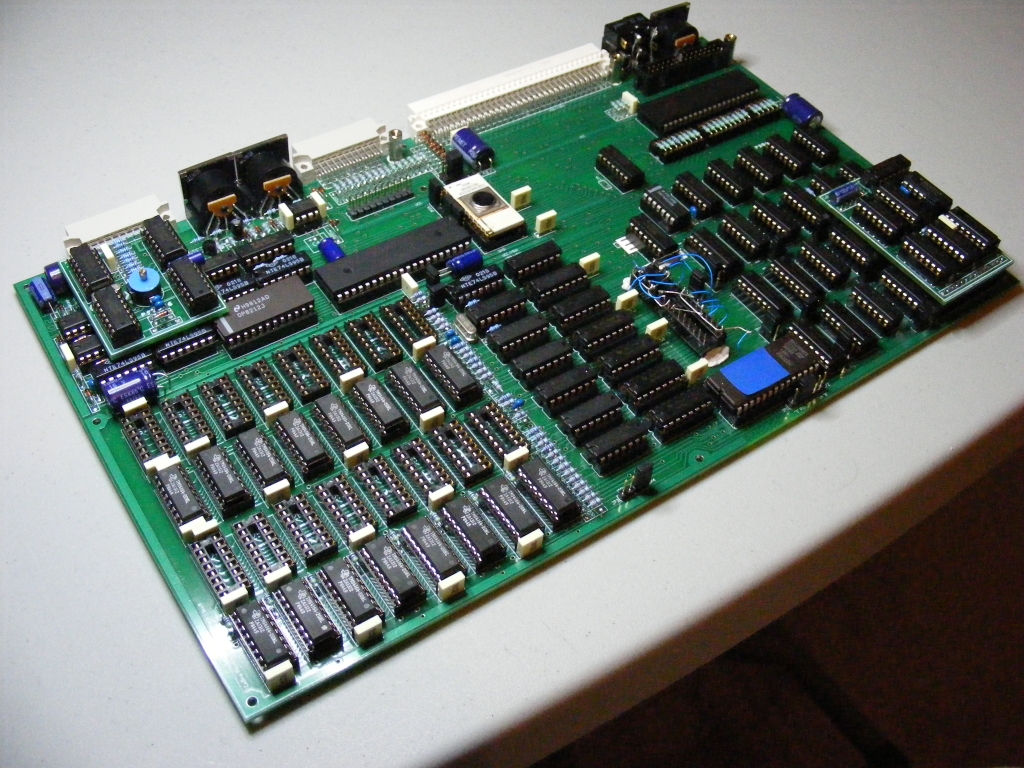

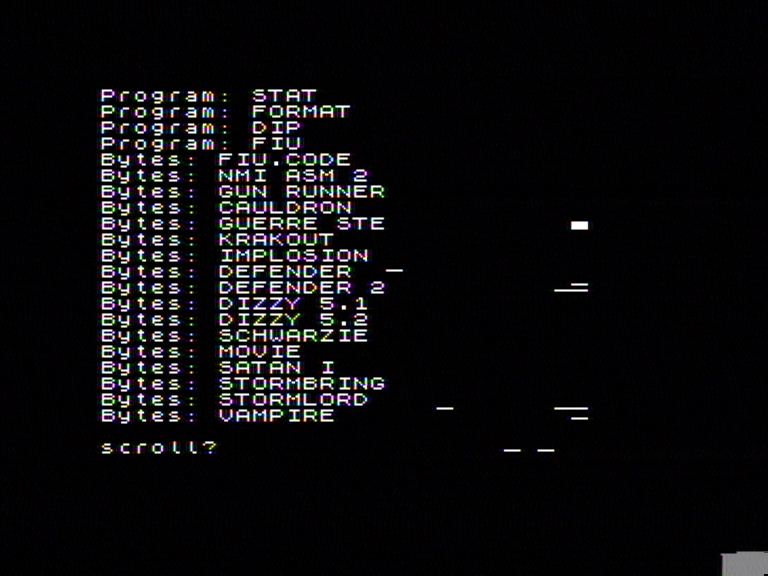

- Un condensator neprevăzut în schemă dar a cărui necesitate a fost determinată experimental, cu valoare de 150 pF, cuplat direct pe pinii 4 ai memoriilor dinamice (bancurile #0, #2 si #3) pentru introducerea unei întîrzieri pe semnalul de RAS (şi ca efect secundar si pe CAS) la memoria sistem. (pag.8 - Circuitul memoriei dinamice 1/2). Practic e vorba de un condensator care să ajusteze timing-ul semnalelor de RAS şi/sau CAS la memorie pentru obţinerea unui acces corect la memoria dinamică (sistem). Acest condensator a fost necesar atunci cînd am folosit pentru memoria sistem cipuri MMN4164-3 fabricate de Microelectronica. Nu ştiu exact ce timp de acces au, dar catalogul spune că e între 200 şi 300 ns. Am făcut apoi teste şi cu cipuri de memorie DRAM TMS4164-20 pentru memoria sistem. Ei bine, cu astea n-a mai fost nevoie să pun nici un fel de condensator de întîrziere pe RAS sau CAS la memoria sistem. De unde am tras concluzia că memoriile cu timp de acces de 200 ns sînt memoriile DRAM ideale pentru CoBra. Am să fac aici o paranteză şi am să redau un screenshot mai jos, care descrie ce se va vedea pe ecran atunci cînd accesul la memoria dinamică sistem nu este corect reglat şi se încearcă încărcarea Basic, Devil, Opus sau altceva de acest gen cu tasta B din configuraţia de start:

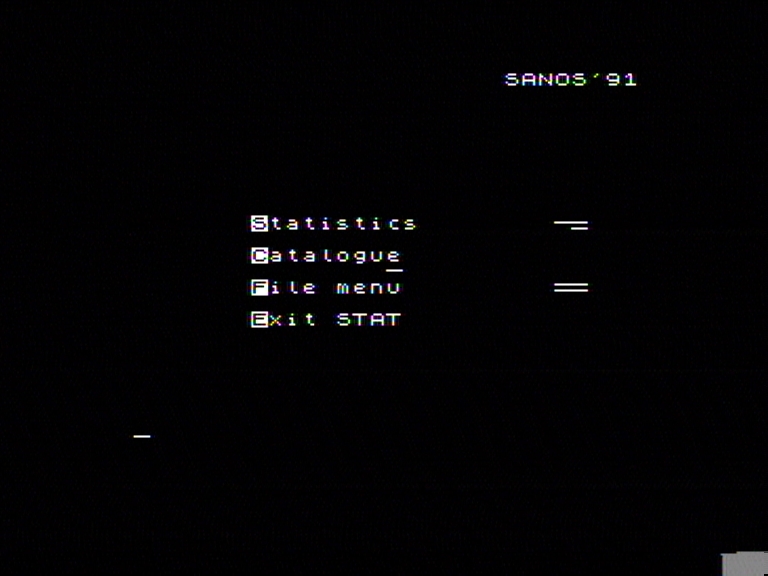

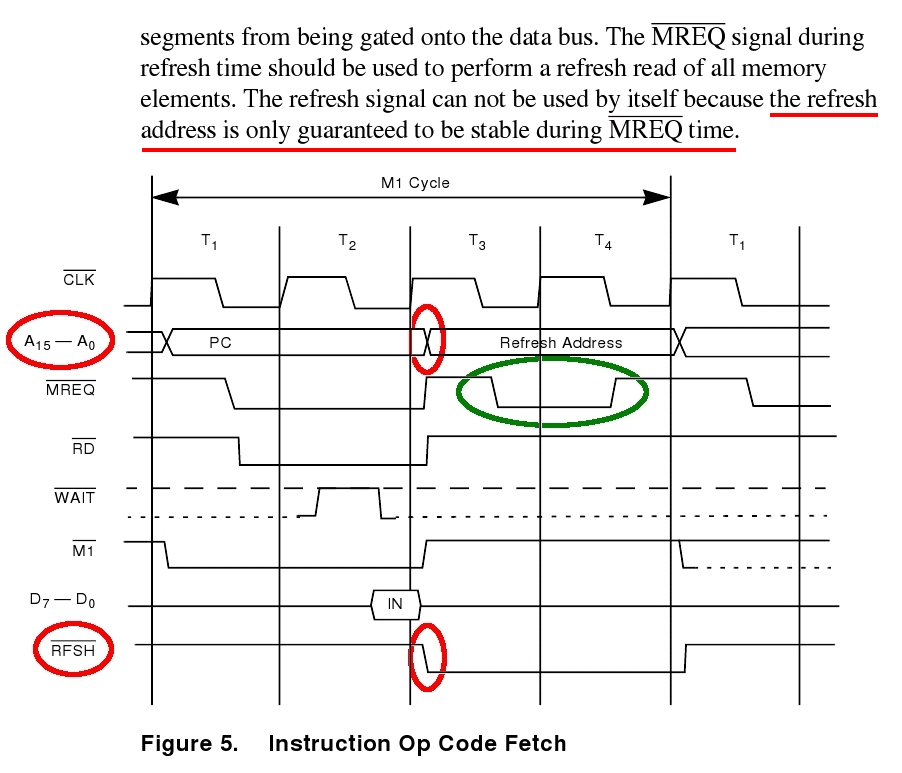

- Un condensator (de asemenea neprevăzut în schemă), cu valoare de 150 pF, cuplat între masă şi pinul 3 al U36 (pag.3 - Circuitul de configurare şi selecţie). Acesta a fost necesar pentru întîrzierea semnalului RFSH astfel încît frontul negativ al BNRFSH de la procesor să ajungă la intrarea de tact U36/3 (inversat prin U53/2) DUPĂ ce bitul 7 al registrului R din procesor a fost pus pe linia de adresa BA7 şi stabilizat. Pentru a explica mai in detaliu, am să repet ce spune manualul hardware CoBra: la pornire, în configuraţia de start, registrul R din procesor are bitul 7 setat pe 1. Apoi, în momentul apăsării unei taste pentru indicarea sistemului de operare ales în continuare, acest bit este resetat pe 0 şi apare pe linia BA7 din magistrala de adrese în timpul primului ciclu de refresh după instrucţiunea care l-a resetat. Momentul este marcat de activarea (trecerea pe "0") a semnalului RFSH generat de procesor. Acest front negativ al BNRFSH este inversat de U53/2 şi transformat în front pozitiv pentru intrarea de tact a bistabilului U36 (7474 foloseste fronturile pozitive de ceas). Deci frontul negativ al BNRFSH ar trebui să încarce bistabilul U36/5+6 cu bitul de date furnizat de linia de adresa BA7. Problema este că dacă ne uităm prin documentaţia oficiala a Z80, aflăm (vezi imaginea de mai jos extrasa din manual, ultima jumătate a ciclului M1) că adresele pentru refresh (BA0-BA7) nu sînt garantate stabile decît pe durata activării semnalului MREQ. MREQ este activat cu o jumătate de clock procesor după ce RFSH e activat, iar RFSH este activat simultan cu punerea adreselor de refresh pe magistrala de adrese.

Cu alte cuvinte, frontul negativ al RFSH apare prea devreme pentru a eşantiona adresele de refresh de pe magistrala de adrese întrucît aceste adrese nu sînt garantate stabile decît o jumătate de clock procesor mai tîrziu. Ce-i drept, schema CoBra are inversorul U53 intercalat pe BNRFSH înainte de U36, iar BA7 este dus direct la U36, deci BNRFSH deja are o oarecare întîrziere faţă de BA7, care în cazul ambelor plăci asamblate de mine pe vremea respectivă a fost suficientă pentru a asigura funcţionarea corecta. Dar acum, cînd am construit acest prototip, dintr-un motiv sau altul această întîrziere n-a mai fost suficientă, şi ce-am constatat practic a fost că atunci cînd apăsam tasta D din configuraţia de start pentru a încărca CP/M de pe disc, border-ul pîlpîia o singură dată scurt pe albastru, revenea pe negru şi apoi calculatorul se bloca, nemaiacceptînd nici o tastă iar unitatea de disc nu mai apuca să roteasca discheta pentru a o citi. Asta din cauză că semnalul LO6, în loc să se menţină pe "1" pentru configuraţia de CP/M, trecea pe "0", lucru determinat cu sonda logică. Din fericire, pe forum l-am întîlnit pe YO3GHM care a avut răbdarea şi amabilitatea să studieze problema de care mă lovisem şi a venit cu ideea salvatoare, un condensator de întîrziere pus pe U36/3 (experienţa îşi spune cuvîntul...). Cum l-am pus, placa de bază a început să încarce sistemul de pe disc corect. Interesant este că în DEVIL (Basic cu disc pentru CoBra) operaţiunile cu discul decurgeau perfect, comenzile CAT şi LOAD nu aveau nici un fel de probleme. Asta pentru că LO6 nu avea probleme să treacă pe "0" (pentru configuraţia de BASIC/DEVIL) ci avea probleme numai cu menţinerea pe "1" (pentru configuraţia de CP/M).